Recently, a research group led by Prof. Cheng Lin from School of Microelectronics, University of Science and Technology of China (USTC) of the Chinese Academy of Sciences has made achievements in the field of fully integrated isolated power chip design.

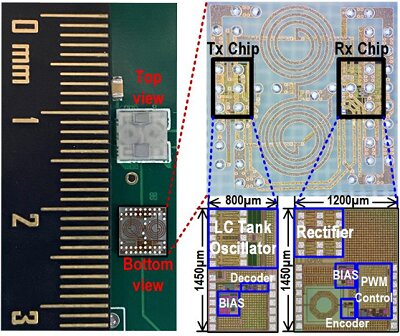

The researchers proposed a chip based on glass fan-out wafer-level package (FOWLP), achieving 46.5% peak transformation efficiency and 50mW/mm2 power density.

Compared with the traditional isolated power supply chip, this new design interconnects the receiving and transmitting chips through the micro transformer made of the rewiring layer, showing no need of additional transformer chips. In this way, it lowered the need for three or even four chips in the existing chip design, so as to greatly improve the efficiency of isolated power supply.

In addition, the researchers proposed a grid voltage control technology with variable capacitor, which maintains the grid peak voltage in the best safe voltage range even in a wider supply voltage range.

This design improves the conversion efficiency and power density of the chip effectively, providing a new solution for the design of isolated power chip in the future.

This work is published at the IEEE International Solid State Circuits Conference (ISSCC), and was selected as the demo demonstration at the meeting.